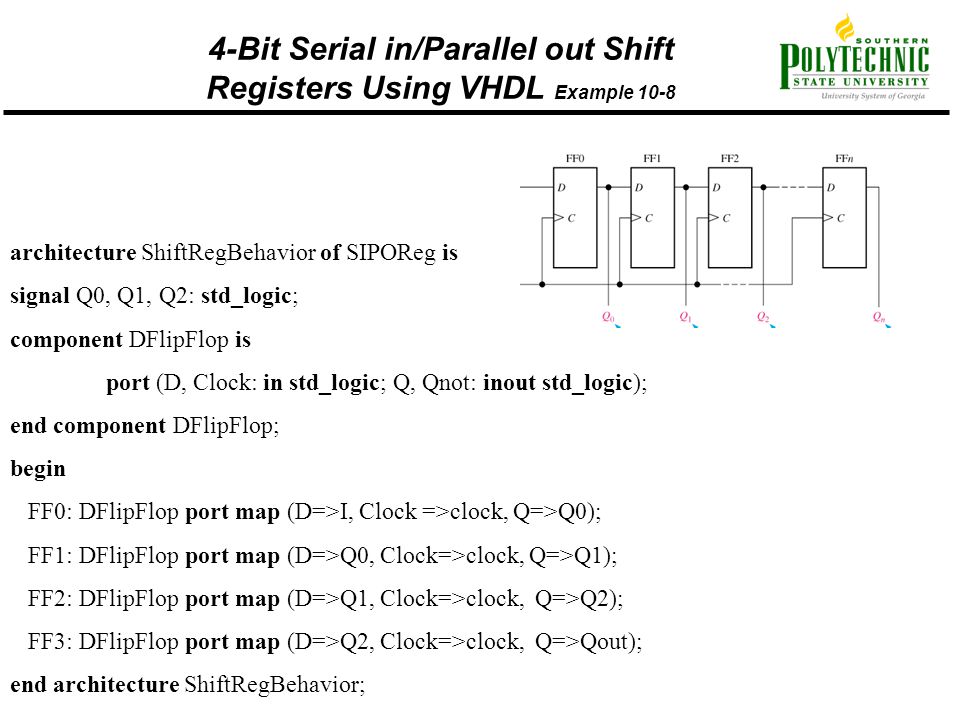

#8 bit parallel in serial out shift register vhdl code codeFor example, you could just change the definition of tmp to be bigger and the rest of the code will just automatically adjust (except for the initialization to "10000001"). This really doesn't matter for this code, but when you start doing bigger things then these will help you a lot. The next thing is my use of 'high and 'low instead of hard-coding the values. This is considered to be better than using 'event. This is a new-ish thing to VHDL and isn't covered in some of the VHDL books. The first thing is my use of "rising_edge()". The changes I made are minor, for sure, but important. Tmp <= tmp(tmp'high-1 downto tmp'low) & "0" - '0' and "0" are equivalent in this context Your code is currently this: process (C, ALOAD)īut should look like this: process (C, ALOAD) Please keep in mind that I'm not trying to be critical or harsh- I'm just trying to get you up to speed quickly. This made it easier to see it on o-scope. while(1)īit_clear(PORTB,BIT(CS)) // Low Chip Selectīit_set(PORTB,BIT(CS)) // High Chip select Triggered at falling edge.ĮDIT: Forgot to add, this is my cleaned up AVR code now. Triggered at rising edge.īottom waveform: Clock. Here are the waveforms from the scope.īottom waveform: Clock. When I set it back to 0, the data was 100000010 instead of 10000011. When I was debugging before, I inadvertently set CPHA bit to 1. I've made a slight improvement such that 10000001 no longer comes out as 10000011 but instead is 10000010. #8 bit parallel in serial out shift register vhdl code serialFor all screenshots, the serial out was the same (10000001). It was only after I confirmed that it was working ok that I started work on the SPI interface which is where things went wrong. Not only that, I've even clocked it via the AVR. That showed no problems whatsoever and the register spat out bits serially just fine. I've been at it for the past 8 hours or so to no avail.ĪDDED INFO: Initially, when I programmed the CPLD I tested it via the buttons on my development board. #8 bit parallel in serial out shift register vhdl code how toI'll appreciate any sort of pointers on how to solve this issue. Could this error have something to do with breadboards? I've run out of photoresist copper clads so can't make a PCB just yet. I'm running it at the lowest possible frequency i.e. but how am I supposed to set up the CPLD such that this is not an issue? My clock is not very fast. I've tried to read up on them but don't seem to quite get it. Note that I'm quite new to VHDL/CPLDs and I keep running across something regarding timings and how critical they are. Tmp <= tmp(tmp'high - 1 downto tmp'low) & '0' Signal tmp: std_logic_vector(7 downto 0) Which I was hoping would provide less room for error. I'm hardcoding the input as then I don't have to mess around with additional wires. Note that I've intentionally left out the input.

PORTB = 1 // This loads the shift register.Īnd this is the VHDL code I'm using. The following is the code for my AVR int main(void)ĭDRB = (1 << DD_MOSI) | (1 << DD_SCK) | (1 << 2) | (1 << 0)

What could be causing this? Thinking it could be my VHDL code, I've even copy pasted other people's codes from the web to see if it works but unfortunately I get the same results. Shouldn't the serial output become 0 on the 2nd clock cycle? The top waveform is the serial output from my shift register and the bottom waveform is the clock.

I've attached the picture to illustrate this. This is also reflected in my oscilloscope. However, if the input to the PISO register is 10100000, the AVR reads in the data as 11100000. In this case, the AVR reads in the data correctly.

Suppose I have an input which contains only one set bit i.e. I'm using SPI to interface with the CPLD using my AVR. I've implemented a 8-bit Parallel in Serial Out (PISO) Shift register in VHDL on my Max V CPLD.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed